Institut für Informatik Lehr- und Forschungseinheit für Kommunikationssysteme und Systemprogrammierung

Ludwig-Maximilians-Universität München

# Evaluation of Task Scheduling Algorithms and Wait-Free Data Structures for Embedded Multi-Core Systems

Master Thesis

Tobias Fuchs Matrikel-Nummer 10393480

BetreuerDr. Karl Fürlinger (LMU)<br/>Dr. Tobias Schüle (Siemens AG)AufgabenstellerProf. Dr. KranzlmüllerBearbeitungszeitraum01. April 2014 - 14. Oktober 2014

Tobias Fuchs: *Evaluation of Task Scheduling Algorithms and Wait-Free Data Structures for Embedded Multi-Core Systems* October 14, 2014

This work is licensed under a Creative Commons Attribution-ShareAlike 4.0 International License.

SUPERVISORS: Dr. Karl Fürlinger (LMU) Dr. Tobias Schüle (Siemens AG)

LOCATION: Munich, Germany

TIME FRAME: April - October 2014 *Ohana* means family. Family means nobody gets left behind, or forgotten.

— Lilo & Stitch

Dedicated to Corinna and my grandmother Gabriele.

"For a while" is a phrase whose length can't be measured. At least by the person who's waiting.

- Haruki Murakami, South of the Border, West of the Sun

# Abstract

Scaling computational power on embedded systems is subject to the general restrictions and laws observed in the last decade: Single core architectures having reached their physical limits, the importance of multi-core systems also grows in the embedded domain. Wait-free progress conditions appear to be a perfect match for the demand for bounded execution time in time-critical applications. However, strong progress guarantees are even more challenging to achieve when real-time constraints apply to the implementation of data structures. This thesis examines the state of the art of non-blocking and wait-free algorithmic paradigms with respect to their applicability in embedded- and real-time applications. Existing wait-free data structures are modified to enable their use in time-critical tasks and compared to prevalent lock-free alternatives in performance evaluation. In a complementary chapter, a comparison of work-stealing strategies gives an outlook from data- to task parallelism.

# Declaration of originality

I hereby declare that I have produced this paper without the prohibited assistance of third parties and without making use of aids other than those specified; notions taken over directly or indirectly from other sources have been identified as such.

**Tobias Fuchs**

City, Date

# Acknowledgements

I sincerely thank my advisor Dr. Karl Fürlinger at the Ludwig-Maximilians-Universität München for his outstanding support and caring attitude throughout the course of this thesis.

I would like to express the deepest appreciation to the outstandingly skilled team at the multicore expert center at Siemens AG Corporate Technology. Results in this work would not have been possible without the persistent guidance and rich knowledge of my advisor Dr. Tobias Schüle and Dr. Christian Kern.

I owe my gratitude to Dr. Thomas Zander who introduced me to his project and gave me the opportunity to work on fascinating problems with such exceptionally bright minds.

# Contents

| 1 | 1 Introduction |          |                                                                   |    |

|---|----------------|----------|-------------------------------------------------------------------|----|

|   | 1.1            | Proble   | m statement                                                       | 1  |

|   | 1.2            | Object   | ives and contributions                                            | 2  |

|   | 1.3            | Structu  | are of this thesis                                                | 2  |

| 2 | Wai            | t-free d | lata structures                                                   | 3  |

| - | 2.1            | Introd   |                                                                   | 3  |

|   |                | 2.1.1    | Definition of wait-freedom                                        | 3  |

|   |                | 2.1.2    | Motivation                                                        | 4  |

|   |                | 2.1.3    | Theoretical foundations                                           | 5  |

|   |                | 2.1.4    | Technical foundations                                             | 7  |

|   | 2.2            | Relate   | d work                                                            | 12 |

|   |                | 2.2.1    | Universal construction of wait-free data structures               | 13 |

|   |                | 2.2.2    | Simulation of wait-free data structures and the helping mechanism | 13 |

|   |                | 2.2.3    | Memory management                                                 | 14 |

|   |                | 2.2.4    | Queues                                                            | 17 |

|   |                | 2.2.5    | Lists                                                             | 18 |

|   |                | 2.2.6    | Stacks                                                            | 18 |

|   | 2.3            | Verific  | ation and benchmark methodology                                   | 19 |

|   |                | 2.3.1    | Explicit-state model checking                                     | 19 |

|   |                | 2.3.2    | Benchmark methodology                                             | 21 |

|   | 2.4            | Pools    | •••                                                               | 25 |

|   |                | 2.4.1    | Definitions                                                       | 25 |

|   |                | 2.4.2    | Array-based wait-free pools                                       | 27 |

|   |                | 2.4.3    | Thread-dependent search patterns                                  | 28 |

|   |                | 2.4.4    | A compartment-based index pool                                    | 29 |

|   |                | 2.4.5    | Verification                                                      | 29 |

|   |                | 2.4.6    | Benchmarks                                                        | 30 |

|   |                | 2.4.7    | Evaluation                                                        | 31 |

|   | 2.5            | ~        | S                                                                 | 32 |

|   |                | 2.5.1    | Definitions                                                       | 35 |

|   |                | 2.5.2    | Adapting the Kogan-Petrank wait-free queue for embedded systems   | 35 |

|   |                | 2.5.3    | Benchmarks                                                        | 41 |

|   |                | 2.5.4    | Evaluation                                                        | 42 |

|   | 2.6            | Stacks   |                                                                   | 44 |

|   |                | 2.6.1    | An efficient wait-free stack for multiple producers and consumers | 45 |

|   |                | 2.6.2    | Verification                                                      | 47 |

|   |                | 2.6.3    | Evaluation                                                        | 48 |

| 3 | Task           | c Sched  | luling                                                            | 51 |

|   | 3.1            | Introd   | uction                                                            | 51 |

|   |                | 3.1.1    | Technical foundations                                             | 51 |

|   |                |          |                                                                   |    |

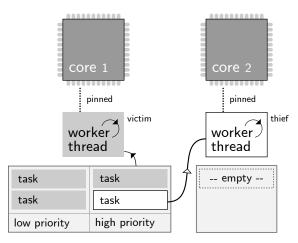

|              | 3.2                                                                                                                   | 3.1.2Related WorkWork-stealing with prioritization | 52<br>52       |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------|--|

| 4            | Sum<br>4.1<br>4.2                                                                                                     | nmary<br>Revisiting the objective                  | 55<br>55<br>55 |  |

| Bibliography |                                                                                                                       |                                                    |                |  |

| Appendices   |                                                                                                                       |                                                    |                |  |

| A            | A List of Figures                                                                                                     |                                                    |                |  |

| В            | Code listingsB.1 Implementation of the modified Kogan-Petrank queueB.2 Implementation of the modified wait-free stack |                                                    |                |  |

# **1** Introduction

Among all computer systems that increasingly become a part of everyday life, embedded systems most probably have the highest impact on our personal safety. By definition, they interact with physical processes and therefore must meet real-time performance criteria. As technical components in risk-classified domains such as transportation and healthcare, embedded system applications are comprehensively audited for fault-tolerance, and characteristic constraints on resource consumption and execution times apply to the design of algorithms and data structures.

To harness the computational power of multi-core processors, applications must be parallelized, yet few existing libraries comply with constraints in real-time software applications. In addition, classical synchronization mechanisms such as locks introduce potential hazards such as deadlocks and starvation.

According to formal definition, wait-free algorithms provide the strongest possible fault-tolerance and guarantee an upper bound for their execution time.

# 1.1 Problem statement

Related work on wait-free data structures does not consider suitability for embedded systems and employ mechanisms such as garbage collection that conflict with wait-freedom or are not easily implemented using restricted resources. Applicationready implementations of wait-free concurrent data structures are therefore of high relevance for embedded system software engineering, especially for hard real-time applications.

In this master thesis, wait-free data structures and task scheduling algorithms shall be investigated regarding their suitability for embedded systems. This includes the following tasks:

- Literature research and analysis of existing approaches

- Development of appropriate algorithms and data structures

- Analytical derivation of upper bounds on the timing behavior and memory consumption

- Preparation of benchmarks and experimental evaluation on different hardware platforms

- Documentation and presentation of the results

# 1.2 Objectives and contributions

We present an overview of state of the art approaches and methodologies in wait-free data structures and algorithms, and practicable solutions for real-time and embedded system applications. In addition, intra-task scheduling is evaluated in variants of work-stealing strategies.

Characteristics of algorithms in real-time and embedded system applications are explained, and how they differ from general purpose software. Existing solutions are discussed with respect to their adequacy for real-time software.

Most relevant for practical use, this work contains application-ready implementations of a wait-free concurrent pool, queue and stack that are meeting requirements of time-critical applications.

For data structures, means of automated verification derived from their semantic definition are explained.

Evaluation of data structures in this work follows the principles of existing publications as close as possible to keep results comparable to related work. Differing from most existing performance comparisons, additional custom test scenarios emphasize metrics that are relevant to embedded- and real-time applications in particular, such as maximum latency and jitter. To illustrate the overall performance implications of wait-freedom, a popular lock-free implementation of each data type is added to the candidate set of its wait-free alternatives.

In addition, the benchmark framework implemented over the course of this thesis is explained in detail. Measurements in publications on lock-free and wait-free data structures are typically impossible to reproduce as little insight in the setup and implementation of the test tools is delivered. However, reproducible and precise performance measurements are only rendered possible by intricate detail, and ideally take platformdependent behaviour into account.

# **1.3 Structure of this thesis**

Concurrency in algorithms manifests in two main aspects: Data parallelism and task parallelism. Correspondingly, wait-free data structures and task scheduling are discussed in separate chapters of this thesis. Both start with an introductory section covering theoretical and technical foundations behind the problems and approaches presented. Existing publications that have been starting positions for own approaches are discussed in a separate section on related work in both chapters.

The sections following the review of related work describe own findings and results that have not been presented in previous publications. Verification and performance evaluations put own implementations in comparison to the status quo of lock-free algorithms.

# 2 Wait-free data structures

In this chapter, an introduction to progress definitions is provided along with other formal foundations for wait-free algorithms and data structures. This includes their theoretical relevance for requirements in embedded and real-time computing, and how wait-freedom is helping applications to guarantee task completion to critical dead-lines.

In the following, concrete implementations of common data structures are presented with respect to their dependency on micro-instructions. Finally, these implementations will be verified and compared using benchmarks representing real-world demands.

# 2.1 Introduction

What guarantees could a data structure provide on the duration of its operations? For sequential algorithms, we consider duration of an operation as an unconditional consequence of its run-time complexity. Structural analysis gives reliable guarantees on worst-case complexity in the *O* domain, and estimating upper bounds for data structures is a daily routine in software engineering.

In concurrent data structures, the concept of duration unfolds into additional dimensions. Operations might depend on scheduler characteristics, and deadlock situations can delay the most efficient algorithm indefinitely. To account for these aspects, guarantees on execution time and completion of operations on concurrent data structures are defined in terms of *progress*.

In addition to their ranking by run-time complexity, concurrenct algorithms form a hierarchical structure of *progress guarantees*, with wait-freedom as the strongest guarantee in the classification.

This chapter summarizes the theoretical background of progress conditions in concurrent data structures, and the technical foundations of their realization.

#### 2.1.1 Definition of wait-freedom

In the following, terms are used according to their common definitions in literature [HS11]: An *object* is an instance of a *data structure*, a container with a specific *state* that implements an abstract *data type*. The data type defines a set of *methods* available to manipulate it. An *operation* to an object is a single *execution* of a method according to the method's *signature*. Finally, data type *semantics* describe the methods' concrete effect on the object, i.e. how they transform the object from one well-defined state to another.

Using these definitions, an implementation of a concurrent object is informally described as wait-free if it guarantees that every process can complete any operation on the object [Her88]

- 1. within a finite number of execution steps, and

- 2. independent from scheduling and the progress of other processes.

This description implicitly includes unconditional fault-tolerance, as any process can complete its operation even if all other processes are aborted. Consequently, concurrency control in wait-free algorithms cannot be based on locks. *Non-blocking* implementations control concurrent access without exclusive access to any resource, which is necessary, but not sufficient for wait-freedom.

Application of the term wait-freedom varies in literature. However, a formal logic designed to verify progress properties of algorithms exists [Don06], and definitions of non-blocking progress conditions have been established in linear temporal logic (LTL) [PMS09].

An upper bound on number of execution steps for any operation is often presumed as a requirement for wait-freedom of shared objects. In fact, wait-freedom requires a *finite* number of execution steps. Existance of a *limit* for execution forms an additional, stronger *bounded wait-free* property. A hierarchy of progress properties is discussed in subsection 2.1.3, with explanations on their differentiation.

### 2.1.2 Motivation

Wait-freedom guarantees progress of a task independent from the scheduler strategy and activity of other processes. On the one hand, any activity by any other process can delay the completion of a wait-free procedure only for a limited number of steps. On the other hand, wait-free algorithms do not rely on progress of other processes. Whenever CPU time is assigned, they are guaranteed to progresss in their task.

This description alone might give the misleading impression of wait-freedom as a general performance improvement. The opposite can be true: For non-blocking implementations, any stronger progress guarantee is earned at the expense of throughput and average case performance. Stronger progress guarantees are bad advice when these metrics have priority and varying worst-case performance is acceptable.

Wait-free algorithms are a solution to adversities that cannot be outrun by efficiency. In a larger scale, they eliminate the common pitfalls in concurrent software engineering, not just by reacting to them properly, but by making their occurrence impossible. Prominent examples are:

**Deadlocks** Processes that cannot proceed because they are waiting for resources that are mutually held by other processes

- **Priority inversion** Low-priority processes hold a lock required by a higher priority process

- **Convoying** Several processes acquire locks in a similar order. If a slow process acquires a lock first, all other processes slow to the speed of the first one, neutralizing their scheduling priority.

- **Kill-sensitivity** A thread is aborted before releasing an exclusive lock to a resource, for example.

Async-signal safety Signal handlers cannot use lock-based primitives, especially malloc and free

These formal guarantees are invaluable for real-time software applications. In this domain, priorities are shifted to fail tolerance and adherence to timing schedules. Then again, specific guidelines and restrictions apply for implementations of time-critical software, especially in embedded software engineering. As a result, most published algorithms cannot be employed in real-time applications in their original form, and have to be modified first. This chapter closes with characteristic constraints in embedded-and real-time software engineering, and how they relate to wait-free data structures and their implementation.

# 2.1.3 Theoretical foundations

Designing wait-free data structures is an ambivalent challenge between complex formal conditions as well as meticulous technical obstacles. This subsection gives an introduction to terms and definitions from theoretical aspects of concurrent algorithms, focusing on progress guarantees and correctness conditions.

# **Classification of progress**

Herlihy and Shavit give concise and comprehensive definitions of progress conditions in their work *On the Nature of Progress* [HS11]. They explain the elementary vocabulary of progress in concurrent methods and continue to construct a unified model for progress conditions using just two aspects: Whether guaranteed progress is minimal or maximal, and how progress depends on scheduling. The combination of both aspects leads to an intuitive classification.

Considering any possible schedule of operations on a shared object, they define *minimal progress* as a condition that guarantees at least one thread to make progress, and *maximal progress* if progress is guaranteed for all threads.

For the second aspect, it is evident how blocking algorithms always depend on scheduling characteristics. Deadlock- and starvation-freedom in blocking algorithms must derive from the assumption that some thread will leave a critical section at some point in the schedule. The non-blocking wait-free and lock-free properties, on the other hand, hold as long as any thread is scheduled at any time, and do not depend on the order of threads in the schedule.

Wait-freedom, the strongest possible condition, is independent from scheduling and guarantees progress for all methods in any execution. The classification criteria correspond to formal definitions previously stated by Petrank in linear temporal logic [PMS09]:

**Definition 2.1.1** (Wait-Freedom). An *execution*  $e \in P$  is wait-free if and only if *e* satisfies

$\forall t \quad (GF sched(t)) \rightarrow (GF prog(t)).$

A program *P* is wait-free if every execution  $e \in P$  is wait-free.

Rephrased informally, program is wait-free if it makes progress in any scheduling of any execution at any time. There is no statement on *how long* a program would have to make progress until completion, yet. In related work, as mentioned earlier, wait-freedom is often used as synonym for a limited number of execution steps for all operations. This requires a further restriction of maximal progress. Petrank defines:

**Definition 2.1.2** (Bounded Wait-Freedom). An execution  $e \in P$  is k-bounded wait-free if the execution satisfies

$\forall t \ GF_k^{sched(t)} \ prog(t).$

A program *P* is *bounded* wait-free if for any  $n \in \mathbb{N}$ , there exists a  $k \in \mathbb{N}$  such that all executions in P(n) are k-bounded wait-free.

It is worth mentioning that the upper bound of steps to completion *k* in any history is not necessarily constant and may depend on other parameters, such as the number of threads or a data structure's capacity. The limit has to exist as a concrete value for any specific execution, though [Her, p. 59].

#### Linearizability and serializability

Correctness conditions are not related to progress or wait-freedom in particular. They prove sequential consistency of concurrent operations in general, i.e. that their semantics are robust in any parallel execution.

Serializability is a correctness condition well-known from databases and distributed computing. Essentially, a scheduling of parallel operations is serializable if the effect of its actions would also result from their sequential execution[Pap79]. Then, a concurrent object is serializable if and only if all schedulings of parallel operations to it are serializable.

Herlihy defined *linearizeability* as an additional correctness condition for concurrent objects [Her91].

Both conditions relate to the problem that operations to an object execute over an interval of time. Without additional conditions granted, the object's state between invocation and completion of an operation is undefined, as its effect might only be partially applied.

A shared object is *linearizable* if every operation appears to take effect instantaneously at any time during its execution. The instant of effect is called *linearization point* of that operation [HW90]. It defines the point in time where the effect of a concurrent operation can be observed by other threads, and separates two observable, consistent states of the object, before and after the operation. This reminds of characteristics of atomic operations and atomicity in the transaction model.

Now, the essential detail is that two linearization points within the same object never occur simultaneously. Also, the amount of time spend in an operation before and after its linearization point is irrelevant. In conclusion, linearization points of concurrent operations indeed describe their equivalent sequential scheduling. In brief: If a linearization point can be found for every method of a shared object, it can safely be claimed to be linearizable. Serializability can only be decided globally by means of possible execution histories of all involved transactions. Linearizability is a condition local to a process. This is convenient, as interactions of threads do not have to be examined when proving wait-free progress. Just like serializability, linearizability states that one or more sequential schedules with identical effect (*linearizations*) must exist for any history of operations on a data structure. The described implications of linearization points are an intuitive way to prove this, and an invaluable in communicaton on correctness.

For overlapping method calls, execution order is arbitrary and corresponds to the order of their linearization points. Otherwise, the real-time ordering of operations must be respected in their linearizations.

Serialization does not define when a transaction must take effect relative to the time of invocation and response. Linearizable operations are required to take effect between their invocation and response, which is a useful restriction for use in real-time applications.

# 2.1.4 Technical foundations

In this work, low-level implementation details are omitted in favor of explanations of algorithmic patterns and theory. Obviously, a comprehensive documentation of a CPU instruction set is readily available, while new paradigms in data structures are hard to elaborate.

This section covers technical foundations that are essential prerequisites for lock-free data structures, but does only explain details necessary to understand implementations presented in this work.

## Fundamental atomic read-modify-write instructions

The vocabulary available to phrase non-blocking algorithms consists of a surprisingly small set of processor instructions. All of them realize atomic operations on one variable in a read-modify-write cycle.

The conditions that define whether a single atomic instruction is available on a specific platform do not follow a predictable pattern. Non-blocking algorithms are inseperably coupled with low-level computation, and many elegant approaches are known to fail on a wide range of platforms. In fact, more than just a few algorithms have been published that are known to be disfunctional on conventional processing architectures, as they depend on exotic instruction sets of special purpose architectures.

The following gives a brief description of the most significant read-modify write operations with their semantics, and the architectures that support them [JP06]:

**LL/SC** abbreviates the pair of instructions *load-linked* (LL) and *store-conditional* (SC). An additional operation *validate-link* (VL) is typically implied. LL/SC is available on ARM, MIPS, and Alpha architectures.

• LL(R) returns the value of register R.

- SC(R,v) changes the value in register R to v and returns true, if and only if no other process performed a successful SC since the most recent call of LL of the current process. Simply put, SC fails if the value of the register has changed since it has been read.

- VL(R) returns true if no other process performed a successful SC on register R, which allows to test a register value without changing it.

**RLL/RSC** is the reduced variant of load-linked / store-conditional. Semantics are weaker than LL/SC, as spurious failures are permitted for RSC where SC would succeed, and no shared variables must be accessed between the latest call of RLL and RSC.

**CAS** is an umbrella term for Compare And Swap instructions which modify a variable if and only if its current value is identical to an expected value. Nowadays, CAS is supported on Intel x386, x64 and most general purpose architectures with operands are restricted to pointer size.

- CAS(R, e, n) returns true and sets the value of R to n if the value in R is e. Otherwise, it returns false.

- extended CAS is identical to regular CAS but the expected value is passed by reference and set to the variable's previous value on success. This signature is most prevalent in academic literature and can be easily derived from regular CAS.

- DWCAS, "Double-Wide" CAS, performs CAS on two adjacent memory locations and is available on most modern x86 and x64 architectures via opcode CMPXCHG16B.

- DCAS (CAS2), frequently confused with DWCAS, performs CAS on two independent memory locations. Despite of being used in some published algorithm designs, it only supported on Motorola 680x0.

**Fetch-and-Add** increments the value of a variable by a given offset and returns the result. This instruction always succeeds.

Both Compare-And-Swap and LL/SC might appear to execute the same task with different semantics: updating a value atomically if some other thread did not succeed first in doing so. The mechanism of a link that is invalidated when a register is changed is, however, fundamentally more powerful.

Compare-and-Swap only allows to test against a value. A use case requires to first read the value of a shared variable to a local copy. CAS is then called with the local variable as expected value and the new value to store. But what if between reading and updating the shared variable other threads changed the value, and eventually set it back to its original state? The comparison with the expected value passes, so the CASoperation modifies the shared variable and succeeds, with no indication for intermediate change.

This situation is known as the *ABA problem* in multithreaded computing. Considering the scheduling in Figure 2.1 as an example.

If a value is changed from A to B, and finally back to A between reading and CASupdating a value, no change is detected. Especially in data structures, atomic variables represent a global state, such as next-pointers in a linked list. Interleaving changes affect

| Thread 1                                    | Thread 2                                 |  |  |

|---------------------------------------------|------------------------------------------|--|--|

| A = read(atomicObj)                         |                                          |  |  |

|                                             | A = read(atomicObj)                      |  |  |

| new = A + 1                                 |                                          |  |  |

|                                             | B = A + 22                               |  |  |

|                                             | CAS(&atomicObj, &A, B) $ ightarrow$ true |  |  |

|                                             | CAS(&atomicObj, &B, A) $ ightarrow$ true |  |  |

| CAS(&atomicObj, &A, new) $\rightarrow$ true |                                          |  |  |

Figure 2.1: Interleaving operations of two threads illustrating the ABA problem

consistency, and in an ABA-hazard, the same value represents two different states of the data structure object.

This problem does not exist for LL/SC, as the first change from A to B invalidates an existing link to the register, and a subsequent SC fails. With only CAS available, hazard pointers or similar reclamation schemes as described in subsection 2.2.3 must substitute the load-linked mechanism.

Publications on non-blocking algorithms often are restricted to either CAS or LL/SC as a prerequisite. Is it possible to port an algorithm to platforms that do not provide atomic instructions it utilitzes?

In theory, CAS and LL/SC can be implemented by means of each other. A lock-free implementation of CAS from LL/SC is shown in listing 2.2 as an example, but no wait-free reverse implementation is known. Jayanti presented wait-free bidirectional constructions of LL/SC and CAS, but makes unrealistic assumptions on semantics of LL/SC with respect to spurious failures of LL/SC [Jay98].

Michael found a wait-free implementation of LL/SC from CAS that is wait-free, albeit in  $O(n^2)$  worst case time complexity and  $O(t^2 + k)$  space complexity for *t* threads and *k* shared objects [Mic04b].

As LL/SC greatly simplifies the implementation of concurrent data structures, research focused on efficient construction of LL/SC from CAS rather than the reverse construction of CAS from LL/SC.

```

1 bool CAS(*addr, e, n)

1 bool CAS_LLSC(*addr, e, n)

2 {

2 {

atomic {

do {

3

3

if (*addr == e) {

if (LL(addr) != e)

4

4

*addr = n;

return false;

5

5

return true;

}

6

6

}

while (!SC(addr, n));

7

7

return false;

// SC succedded

8

8

}

return true;

9

9

10 }

10 }

Listing 2.1: Semantics of Compare-And-Swap

Listing 2.2: Lock-free CAS from LL/SC

```

### Memory consistency

Rarely do programmers have to worry how instructions in source code will eventually be executed on a concrete CPU architecture on micro-instruction level. Compilers and processing architecture have a long history of robust optimization techniques that are commonly trusted.

Again, the combination of non-blocking algorithms and embedded hardware poses a challenge. Memory operations on general purpose processors can safely be considered sequentially consistent under nearly all circumstances, and concurrent algorithms hence can rely on (semantically) sequential memory consistency. In contrast, instruction order on many prevalent architectures in the embedded system domain is only limited when explicity enforced by memory barriers. Otherwise, load- and store- instructions may be executed out-of-order and cause memory access hazards.

The following consistency models are common in literature:

| Sequential consistency | guarantees all reads and all writes are in-order.          |

|------------------------|------------------------------------------------------------|

| Relaxed consistency    | essentially only prevents dependent loads, but allows some |

|                        | reordering of regular loads and stores.                    |

| Weak consistency       | allows any reordering of reads and writes and is only lim- |

|                        | ited by memory barriers.                                   |

Memory consistency is typically either ignored in algorithm-centered publications, or presumed to be sequential for didactic brevity in literature. In reality, sequential consistency that prevents any reordering of instructions on memory is not easily achieved. Code optimization in compilers might weaken consistency even before execution and must be explicitly disabled.

Strict sequential consistency is usually abandoned already in compilation, were a vast amount of optimization techniques involves reordering of memory reads and writes. Explicit keywords like volatile in C (not to be confused with the Java keyword with the same name) allow to annotate code sections that depend on exact instruction order.

Even with correct instruction order in the binary executable, the processor architecture might take the liberty to manipulate memory access order in execution. The following table lists an excerpt of memory reorderings on ARMv7, AMD64 and x86.

| CPU    | Ld/Ld | Ld after St | St/St | St after Ld | atomic after St | dep. Ld/Ld |

|--------|-------|-------------|-------|-------------|-----------------|------------|

| ARMvZ  | 7 yes | yes         | yes   | yes         | yes             | no         |

| x86/x6 | 4 no  | no          | no    | yes         | no              | no         |

| AMD64  | 4 no  | no          | no    | yes         | no              | no         |

As mentioned initially, memory access on general purpose architectures like x86/x64 can almost be treated as sequentially consistent. In contrast, ARMv7, the most relevant CPU architecture for embedded applications in this comparison, essentially knows no restrictions on order. This allows aggressive optimization techniques at runtime, but critical order must be enforced manually using *memory barriers*. Barriers (also: fences) are instructions that, once reached in execution, force a all CPUs to complete a specific kind of memory operation before proceeding. The barrier instruction itself is often written in verbatim inline assembly and must be guarded from compiler optimization. Typical memory barriers are:

SFENCEforces all stores to memory to complete before the next store operation.LFENCEforces all loads from memory to complete before the next load operation.MFENCEforces any access to memory to complete any following memory access.LOCKimplicitly has MFENCE as side-effect.

Finally, cache coherence and memory consistency might have less drastic consequences for implementation of concurrent algorithms after all: Non- blocking algorithms are designed to coordinate access to global states using atomic read-modify-writes. Atomic instructions automatically establish a full fence and clear the cache line of their operands. In most cases, these implicit effects suffice to avoid consistency hazards.

#### Memory contention and false sharing

Local caches reduce memory access time of processors by several orders of magnitude, but their contents must be kept consistent. For cache-coherent multiprocessors, local caches are organized in regions of equal size. These *cache lines* are invalidated as a whole if they differ from the latest value stored.

Slight differences in concurrent algorithms can make a considerable difference on how much a program benefits from processor caches. Consider a simple lock, a shared variable used for central coordination of threads. Assuming that the variable is read and modified by every thread in a loop. Any modification of the object's state invalidates at least one cache line on every CPU core, in effect causing a cache miss whenever the object is read.

A specific usage pattern known as *false sharing* causes avoidable cache invalidation and is notorious for degrading performance: Assuming two separate shared objects that are unrelated in an algorithm's model. If two threads operate on one of the objects exclusively, there are no mutual effects and no memory contention should occur. However, if the objects are stored in memory locations that fall into the same cache line, any modification of one object invalidates the cache line that includes the other. The typical countermeasure for false sharing is to instruct the compiler to align and pad objects into memory regions of the size of a cache line. The respective *cache alignment* and *cache padding* keywords vary between compilers.

The phenomenon of degrading memory access times and overhead from conflicting operations with an increasing number of threads is referred to as *contention*, an umbrella term for competing modifications to the same locations in memory. Effects of high contention rates, i. e. a high amount of threads accessing an object at the same time, are often overlooked in algorithm design, especially on simulated computing models. On real hardware, memory access notably affects performance to a degree that can only be estimated in micro-benchmarks [MS07, 1.1.1].

#### Restrictions in embedded- and real-time software engineering

Not all embedded systems host real-time applications, and not all real-time applications are deployed on embedded systems, of course. However, as the term suggests, embedded systems frequently interact with processes in the physical world. A control loop implemented in software periodically responds to its surrounding system. Hard real-time applications operate in high loop frequencies of 1 KHz and more, and even extremely rare or slight variances in their response frequency might build up unrecoverable instability or result in other functional failures, like loss of image data from a medical scanner.

The scheduled time of the next response is a critical deadline that must be met at all cost. Software engineering in the real-time domain is understandably governed by the concern for deterministic task execution.

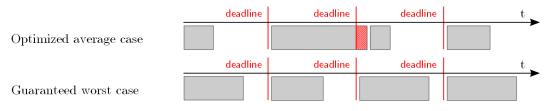

Figure 2.2: Periodical task execution times, optimized average case versus guaranteed worst case

As a consequence, algorithms employed in embedded- and real-time applications are optimized for guaranteed worst-case complexity as opposed to best average-case performance, as illustrated in Figure 2.2. Despite limited resources and the demand for low power consumption, predictable performance is preferred to optimizations of the common case when facing critical deadlines.

In addition, embedded devices often are physically integrated in systems with long maintenance intervals of possibly several years, or difficult to access, raising high stability and fault-tolerance to formal requirements. Therefore, common algorithmic practices might render unusable due to otherwise acceptable risks of failure.

Industrial guidelines for embedded- and real-time software engineering, such as MISRA-C and JSF C++, state variants of the following restrictions:

**Dynamic memory allocation** is guaranteed to introduce non-deterministic delays. Allocation complexity depends on available space and heap fragmentation, which cannot be avoided in general. To prevent delays in critical loops, a fixed-size memory area is allocated in the initialization phase of the application, before performing any time-critical tasks. The principle of worst-case optimization also applies to memory consumption: because later allocation at run time is forbidden, the potential maximum of memory required has to be allocated.

**Garbage collection** mechanisms obviously contradict determinism, but are also prone to memory leaks, especially when in continuous duty over long periods of time.

**Standard libraries** such as the C++ STL use dynamic memory allocation indirectly, and have to be replaced by alternatives specifically tailored to real-time constraints.

**Monotonic counters** are part of many algorithms, with the risk of overflow argued as astronomically low. In long-running systems, however, this probability steadily increases.

# 2.2 Related work

This section summarizes prior publications on wait-free data structures and foundations that are relevant to their design and implementation. Applicability of existing approaches and necessary modifications for real-time systems are discussed in brief.

# 2.2.1 Universal construction of wait-free data structures

In a work that was later awarded with the Dijkstra Price, Maurice Herlihy presented a novel systematic construction of wait-free algorithms in 1991 [Her91], three years after he conducted a proof that all algorithms can be implemented wait-free [Her88]. A universal construction procedurally transforms arbitrary sequential objects into wait- free counterparts. The wait-free algorithms produced by Herlihy's pioneer methods might not be known for their efficiency, but they represent a tangible example for the formal proof that wait-freedom can be achieved for arbitrary shared objects.

Since then, several further universal constructions have been developed. Recent work aims for improved performance of universally constructed algorithms. Fatourou obtained an efficient wait-free universal construction named *P-Sim* [FK11]. The proposed implementation of the P-Sim algorithm uses tagged pointers and therefore must be adapted for embedded and real-time applications. We evaluate a wait-free stack based on P-SIM in section 2.6,

Kogan and Petrank described the *fast-path / slow path* method [KP12], an implementation strategy where operations on a data structure are performed as a cheap lock-free operation first, falling back to a slower wait-free operation if it fails. Data structures based on this strategy showed performance results close to their lock-free counterparts.

Apart from achievements in practical wait-freedom, the fundamental theoretical implications of wait-freedom are subject to ongoing research. In 2012, Ellen, Faith and Fatourou proved that the property of disjoint access on a data structure is mutually exclusive to the wait-free property, with fundamental implications for future approaches in wait-free constructions [EFK<sup>+</sup>12].

## 2.2.2 Simulation of wait-free data structures and the helping mechanism

Only recently, Timnat and Petrank presented a new variant to derive wait-free algorithms from existing lock-free implementations [TP14]. Universal constructions utilize small algorithmic building blocks to rework sequential objects gradually. In what they call a *wait-free simulation*, Timnat and Petrank rather employ a modular and, in some cases, less invasive refacturing scheme.

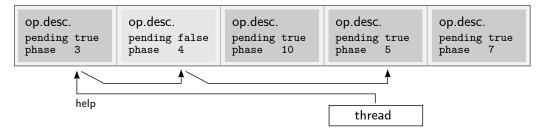

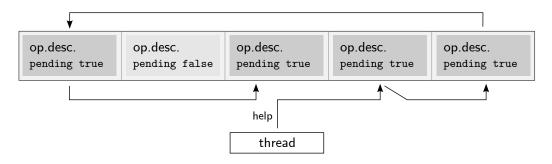

Wait-free simulation is an advancement from a helping scheme which is first known from a publication by John Turek at IBM in 1992 [TSP92]. The mode of thought in recently presented helper schemes follows the basic principle presented by Turek.

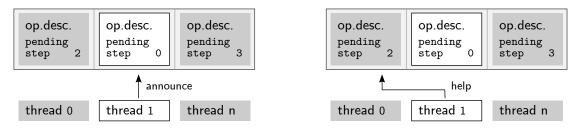

A single lock-free operation, such as adding or removing an element, first is transformed into linearizable, subsequent stages. The operation is then called a *normalized* algorithmn. These sub-steps are partial applications of an operation, but leave the data structure in a well-defined, consistent state. Also, operations are not executed directly, but only announced: the state of a pending modification is stored in an operation description object that then contains sufficient information to complete a single pending modification on the data structure. As a result, every thread can help complete any pending operation by performing its next sub-step.

The motivation behind this is to decouple operations from the thread that executes them. As an additional benefit, the state of an operation description preserves partial progress

of an operation, comparable to safepoints as known from transaction management. In case of a conflicting access, an operation is retried starting from its last successful partial execution instead of repeating a single procedure from its beginning until it succeeds as a whole.

Acting in the spirit of wait-freedom, the helping scheme achieves that once a thread announced an operation, it is guaranteed to be completed even if the thread is never scheduled again.

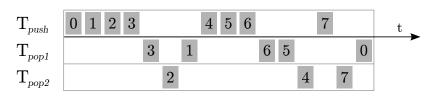

Figure 2.3: Announcing and helping operations in the general helping scheme

As every thread can only initiate one operation at any time at most, one operation description object is required for every thread. These are stored in a global array with every index dedicated to a specific thread. A thread can only modify the data structure by initializing a corresponding description object in the thread's dedicated slot in the array.

An operation description object represents a safepoints on a stable, intermediate states, and is thus only changed when one of their associated substeps has been completed. It is initialized in pending state and marked as non-pending once its last substep succeeded.

A thread only returns from its original operation call when its description object has been updated to the final, non-pending state. However, after they announced their own operation, threads engage in all pending modifications, helping older operations first. New operations on the data structure consequently cannot delay other ongoing operations by more than one substep. This is essential to the guarantee for each operation to be completed in a finite number of steps.

Timnat and Petrank published promising performance evaluations for simulated waitfree data structures. Their candidate algorithms have been implemented in Java and rely on garbage collection, however, and currently no wait-free garbage collector exists. With the intention to deploy wait-free algorithms on long-running embedded systems, this technical flaw is of high practical relevance.

To put it mildly, wait-free memory management offers many opportunities for future work; it has been aptly put as the achilles heel of wait-free data structures, and reasons for this will soon be evident in this chapter.

## 2.2.3 Memory management

A wide range of challenges in concurrent algorithms emerges from memory management within data structures: As memory resources are acquired and read by several threads simultaneously, it is not trivial to decide which accessor is responsible for acquisition and release of a specific memory region, especially when employing the helping pattern as described in subsection 2.2.2.

In software development for embedded systems, garbage collection usually is not provided by the runtime environment. Allocation and reclamation of memory therefore has to be implemented explicitly, and, in the context of this work, with respect to wait-free requirements.

## Memory allocation

The problem of concurrent resource management has been reduced to an abstract data structure named *pool* by Udi Manber [Man86]. Essentially, a pool is an container of objects which abstracts their concrete allocation in memory.

In their book *Concurrent Data Structures*, Moir and Shavit discuss pools as a fundamental tool for concurrent lists and queues [MS07, 1-17]. They mention an array-based implementation and suggest more sophisticated approaches based on counting networks or diffracting trees [SZ96], but do not discuss wait-free variants.

It is important to point out that simulation of wait-free data structures from their lock-free implementation as described in [CER10] and [ZZY<sup>+</sup>13] involves an operation description buffer. Therefore, wait-free algorithms for memory management cannot be constructed using these simulation techniques, as the construction would again rely on a wait-free pool. A scalable lock-free dynamic storage allocator is presented by Michael [Mic04c], which cannot be transformed to a wait-free variant for this reason.

Stellwag and Krainz specifically address wait-free storage allocation and present a design that is apparently suitable for real-time applications [SKSP] which is discussed in subsection 2.4.2

Wait-free memory allocation is rarely even addressed in related work. Most designs of wait-free algorithms are conceptually presented in Java and benefit from garbage collection, leaving wait-free memory management out of scope.

## Memory reclamation

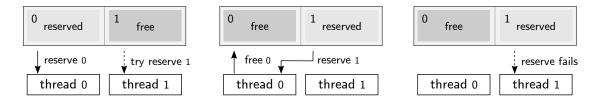

In addition to the problem of concurrent memory allocation, an indirect variant of the ABA problem is introduced when allowing shared memory objects to be reclaimed: After a shared address has been obtained, the referenced object might have been reclaimed and replaced by a new object instantiated at the same address.

A commonly used technique to guard referenced objects from reclamation objects is *reference counting*: A global counter variable is introduced for every shared memory block, which is incremented before referencing it, and decremented as soon as the contained object is no longer used by the respective thread. A shared memory region is consequently released when its associated reference counter reaches 0, as no thread is holding a reference to it at this point. Efficient solutions for lock-free algorithms are known [JP05] [GPST09], and a wait-free mechanism is conceptionally available [Sun05].

Regarding overflow of counters, reference counting methods formally do not solve the ABA problem but only make it unlikely to occur, as an identical counter value may refer to different references.

In a very popular work, Michael introduced *Hazard Pointers*, a patented scheme that allows wait-free memory reclamation [Mic04a, p. 492] relying on available atomic operations *CAS* or *LL/SC*: Each thread operating on a shared data structure owns a fixed amount of hazard pointers. A single active hazard pointer guards one reference at any time, so the amount of hazard pointers per thread depends on the maximum number of simultaneous guards needed in any operation.

When a thread releases a node for reuse, as when removing an element from a linked list, it is not deallocated but added to a local list of retired nodes. Nodes in this list are only deallocated if no other thread is holding a hazard pointer to it. A grace period is implicitly kept, as deallocation is only tried once the retired list reaches a certain size.

The hazard pointer algorithm itself is proven to be wait-free, but has only been presented as a solution in lock-free algorithms. The integration of hazard pointers in wait-free data structures is not trivial in general, and applicability for real-time applications needs additional considerations. How hazard pointers can be used in accordance with wait-freedom has to be examined for each individual case. An example is discussed in detail in subsection 2.5.2, which also includes a proof demonstrating how hazard pointers comply to real-time constraints.

In order to integrate hazard pointers in a data structure, an upper bound for the amount of guarded references for any operation has to exist, and to be known a-priori. Michael demonstrated hazard pointers in lock-free implementations of a list and a stack, where one hazard pointer per thread is sufficient, as no operation needs to guard more than one element. For some implementations of recursively defined data types, e.g. graphs and trees, a maximum amount of guarded nodes per operation does not inherently exist, though. This even poses a problem for much simpler data structures: the original deletion mechanism in Harris linked list requires an arbitrary amount of pointer guards [Har01].

A memory reclamation scheme that overcomes this limitation is known from Herlihy, Luchangco and Moir. Their algorithm *pass the buck* resembles hazard pointers in principle, [HLM02].

A class of reclamation strategies is based on *quiescent states*, i.e system states where an object is impossible to be referenced by another thread. The most prominent example is *Read-Copy-Update*, introduced by McKenney [MS98] and added to the Linux kernel in October of 2002. In RCU, multiple local copies of an object are kept, allowing wait-free reads in single-writer / multiple reader scenarios. Updating the shared object cannot be transformed to wait-free operations, however.

Fraser provided *Epoch-Based Reclamation* [Fra04] as another approach on reclamation involving quiescent states. It avoids expensive memory barriers as required for Hazard Pointers or Pass the Buck. Limbo lists are used to manage retired objects in this strategy, which can be implemented with lock-free, but not wait-free properties. Also, the *EBR* scheme itself is not strictly lock-free, as reclamation depends on progress of another thread and makes assumptions on the fairness of the scheduler. In epochbased reclamation, no objects are deallocated as long as one thread is accessing the data structure.

Several other approaches for memory management in concurrent data structures have been published [Har01], which suffer from dependency on CPU architecture or a certain kind of scheduler.

More recently, Shin, Kim et al. introduced *Strata*, a wait-free memory reclamation scheme based on linked lists and chronological access [SKKE11], and evaluated their solution against user-space *RCU*.

### 2.2.4 Queues

Despite its unimposing functional capabilities, the concurrent queue is the functional core of many data structures. Queues are the most frequently discussed complex data type in publications in the wait-free domain, precisely because of their unsurprising yet indispensabel semantics.

The classic concurrent queue originates from Lesley Lamport in 1977 [Lam77]. The Lamport queue only supports synchronization for a single reader and writer but still is an undisputed solution for this scenario.

Michael and Scott introduced another celebrity among concurrent queue algorithms. The MS-queue is lock-free, and an imperative reference when discussing data structures with queue semantics.

Notable improvements on wait-free queue algorithms are quite recent, with the first practicable solution presented by Kogan and Petrank [KP11] in 2011, which employs a helper scheme with prioritized operation descriptions as described previously to resolve conflicting accesses.

The prioritization of pending operations is achieved using a monotonic counter: Each operation description contains a phase number, interpreted as the operation's timestamp. After a thread has announced its operation, it traverses the operation description and engages in every pending operation with a phase number less than or equal to its own. The phase value of a newly announced operation is thus intended to be greater, thus of lower priority, than phase values of older pending operations. This is argued to be achieved by traversing all elements in the operation description buffer to resolve the current maximum phase, incrementing it, and setting the result as a new operation's phase.

Kogan and Petrank complemented the wait-free queue with the *fast-path / slow-path* methodology [KP12]. It describes the simple yet effective algorithmic pattern to try wait-free operations as a fast, lock- free variant first, and only fall back to a slower wait-free path if it fails. In some benchmark scenarios, a fast-path variant of the Kogan-Petrank queue achieved throughput measurements close to lock-free candidates.

Nearly all published evaluations confirm notable performance gains of wait-free algorithms with an optimistic fast path.

# 2.2.5 Lists

Valois succeeded in the first implementation of a lock-free list that only requires prevalent compare-and-swap instructions [Val95]. Michael and Scott pointed out how the memory reclamation as presented by Valois is prone to an ABA race condition, and also suggested a solution [MS95]. The Valois list is still potentially causing memory leaks in the revised version, and is therefore not evaluated in this chapter.

Comparable to the Michael-Scott queue, Harris' linked list is an established reference for lock-free ordered lists [Har01]. The *Tim Harris algorithm* executes dequeue operations in two stages using tagged pointers. Nodes are first marked as logically deleted and physically deallocated afterwards. This process is not kill-tolerant as a node would never be physically deleted if a thread cancels its operation in the second phase. Michael revised Harris' algorithm and resolved pointer tags and vulnerability to cancellation using his hazard pointer scheme.

Michael improved on Harris' list in his publications on hazard pointers, where tagged pointers and the two stages in the deletion of nodes are replaced by his safe memory reclamation technique [Mic04a].

Timnat and Braginsky transferred the helper scheme and prioritization pattern from Kogan and Petrank's wait-free queue to Harris' linked list [TBKP12]. Although they again only evaluate an implementation in Java, their work presents a practicable design of a wait-free linked list.

An implementation for real-time applications demands additional effort, similar to Kogan and Petrank's queue.

## 2.2.6 Stacks

Treiber proposed a lock-free concurrent stack implementation in which he represents the stack as a singly-linked list. A top pointer for operations on the stack is modified atomically using Compare-and-Swap [DT86].

Jayanti and Petrovic presendet a wait-free stack that supports multiple producers but only a single consumer [JP05].

Hendler and Shavit applied an optimization method to a lock-free stack that benefits from LIFO order [HSY04]. The *elimination* paradigm considerably reduces contention in concurrent data structures and can be applied to any pair of methods that eliminate their effects mututally: An additional execution path mediates between two parallel push and pop operations directly so pop obtains its result from the value argument in push without coordination in the data object. This way, operations that otherwise might conflict can complete even faster compared to their sequential execution, because there is no need to query or modify the state of the data structure in the elimination path.

Moir optimized a lock-free FIFO queue and demonstrated that elimination is also beneficial when it is only applicable for specific combinations [MNSS05] of access collisions. A similar *combining* technique exists that coordinates colliding operations with identical semantics, but is not wait-free in its original design.

Timnat and Petrank mention they have constructed wait-free implementations of the Harris-Linked-List, a skiplist, and a tree, using the aforementioned simulation technique described in the same work [TP14], but did not apply their simulation technique to a stack, where contention is more frequent in comparison as producers and consumers logically operate on the same node. No algorithm code is provided for their data structures. These had to be modified for use in real-time applications in any case, as they rely on garbage collection.

A wait-free stack for multiple consumers and multiple producers is presented in section 2.6 of this work. The implementation builds upon Fatourou's universal construction scheme *P-Sim* which achieves improved scalability using *elimination*.

Bar-Nissan evaluated elimination and combining for blocking and lock-free stack algorithms [BNHS11]. In performance evaluation of stack algorithms in this work, we examine if comparable improvements can be achieved while maintaining wait-free progress.

# 2.3 Verification and benchmark methodology

Meaningful evaluation of algorithms requires to ensure that candidate implementations realize identical semantics, and that identical conditions are used to measure their performance. The means of verifiying semantics and correctness and the setup of the benchmark suite is explained in this section.

## 2.3.1 Explicit-state model checking

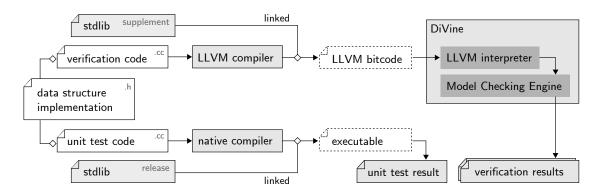

In the software engineering process, testing has evolved as the most common and important method to verify the correctness of a software system against its specification. However, tests are limited to their concrete scenarios by nature and can only indicate correctness for exemplary executions. As conventional unit tests are agnostic of non-deterministic effects, they cannot be applied to specifications of parallel implementations. As testing every possible scheduling of a given set of transactions is not feasible, model-based verification is left as a viable option. In model checking, a system is abstracted as a finite-state automaton corresponding to the system's behavior which is represented and verified logically against a specification, represented by a set of formulas. Elaborating a formal model from an implementation manually - as well as the inverse process - is prone to error and thus can result in critical differences between the source code used in production and the verified model. In addition, code optimizations applied by the compiler can introduce hazards that are not evident in the original source code. Ideally, model checking operates on the compilation result as it is used in the software product's release.

For verification of the data structures presented in this chapter, a tool chain based on the *DiVine* explicit state model checker [BBH<sup>+</sup>13] has been composed. Figure 2.4 illustrates its steps.

The *verification system* is a custom source code implementation designed to execute schedulings that lead to hazard situations in the examined data structure by calling parallel operations on a single instance of it. The system is compiled to LLVM bitcode using the *clang* compiler. In the linker stage, the C++11 standard library is replaced

Figure 2.4: The verification tool chain

by substitutes provided by DiVine that allow detection of memory hazards within the C/C++ runtime and parts of the *STL*.

The logical model for a data structure is derived directly from the LLVM bitcode. For verification, *DiVine's* integrated LLVM interpreter transforms the system to a *nonde-terministic Büchi automaton* (NBA) considering all possible operation interleavings at the level of bitcode instructions. On the NBA's state space, a reachability test on every negated assertion is performed, as well as cycle detection for deadlocks [BK08, p. 159]. A verification run results in a counter-example for the first violated verification property, presented as an operation history of all threads.

DiVine's explicit-state model checking can only verify assertions that are reachable in at least one possible execution history of a program. Source code implementing a verification program resembles unit tests, with assertions on expected values in execution paths. Even with all possible interleavings explored, an incorrect implementation might pass verification if program states that would lead to failures are impossible to be reached in any schedule. It must therefore be argued individually that the verified system is comprehensive enough to produce schedules that provoke all hazard conditions to be tested.

On the other hand, it is advised to design a succinct verification system using the minimum amount of threads and smallest data structure capacity possible. Known as the phenomenon of *state space explosion*, the complexity of verified interaction schedules grows at least exponentially with the degree of parallelism and the amount of concurrent operations in the model. [BK08, p. 77]. Own findings and and related experiments [vdB13] show that rapid growth of the explored state space might render seemingly trivial verification setups impractical. Model checking of 5 or more threads operating on even an arguably trivial shared data structure is not feasible as of this writing [vdB13, p. 46], as its execution might take hours and days; higher degrees of concurrency have not been necessary for this work, however. Instead of monolithic, complex scenarios designed to cover all hazard situations, we define a series of scenarios that are verified individually. In conclusion, the following general process for designing a verification system for a data structure is recommended:

- 1. Declaring white-box conditions as assertions in the implementation of the data structure, i. e. preconditions, postconditions, and loop invariants

- 2. Identifying potential hazards in the data structure

- 3. Deriving critical schedules that would trigger every hazard condition

- 4. Implementation of a verification program that is capable of producing all critical schedules

- 5. Assertions on black box correctness, i. e. expected return values, of the data structure in the verification main program

Still, this procedure provides no guarantee that a positive verification result is *true positive* and evidence for correctness. As explained, a scenario might yield a false positive result if it is insufficient to produce hazard situations in the first place.

A principle known from test-driven development gives a pragmatic solution. Here, complete test scenarios are defined first and performed on a known incorrect implementation. All tests then are expected to fail. Similarily, we first use *DiVine* to detect a counter-evidence that demonstrates a known error in an implementation. This *true negative* result demonstrates how a hazard condition is in fact detectable. As a concrete example, a necessary pointer guard is removed from a data structure. Verification is supposed to disprove correctness and present a counter-example that depends on the missing guard.

As shown in Figure 2.4, a unit test suite is build in addition to the model checking chain. Unit tests are identical to the verification program, but configured with a higher amount of threads and a higher capacity of the data structure. They are executed as a smoke test before starting the *DiVine* chain, as state space exploration might take hours to complete. Once all candidate implementations of a data type have passed the same verification process, their semantics are considered correct and equivalent, a prerequisite for their meaningful comparison.

## 2.3.2 Benchmark methodology

The benefit of an implementation approach can only be reasoned when it is presented with means of a comprehensive comparison to its alternatives. Candidate implementations are embedded in a series of standardized scenarios which have been modeled from real-world load conditions. The resulting performance metrics aggregated from run-time measurements in each scenario give an intuitive understanding of fitness for common application characteristics.

#### **Relevant performance metrics**

A single test case is repeated for every combination of the defined parameter settings range, consequently testing scalability in all dimensions. These are at least the number of elements managed by the test instance and the number of threads operating on the instance. As only a single parameter is modified in every run, variations in performance can be reasoned easily.

Similar to verification systems, benchmark scenarios are modeled based on properties derived from semantics. However, the quality of a benchmark is defined by how closely it is related to real-world applications. Because of this, performance criteria and benchmark task definitions are not formally constructed but derive from common use cases. The following performance measures are a standard in micro-benchmarks of algorithms and data structures in general:

| Timestamps are created right before calling an operation and after its completion. Operation latency is measured as the difference of these timestamps. |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| The overall fluctuation margin of operation latencies.                                                                                                  |

| the total number of operations divided by their overall time to completion,                                                                             |

| measured in operations per second. Throughput is measured individually                                                                                  |

| for every operation type.                                                                                                                               |

| The relation of execution time depending on the number of threads.                                                                                      |

| The same number of operations is executed by an increasing number of                                                                                    |

| processor cores to examine how throughput scales with the degree of parallelization,                                                                    |

|                                                                                                                                                         |

Evaluation of speedup follows the well-known *Amdahl's Law*. For parallelization with *p* as the proportion of a program that is executed in parallel using *n* processors, speedup is defined as:

Speedup(n) =

$$\frac{1}{(1-p) + p/n}$$

Concrete values of p allow to predict speedup for any degree of parallelization, but are unknown for evaluated algorithms a priori. We measure execution time for an identical problem size with an increasing number of cores  $n_k$ . The estimated proportion of parallelizable regions  $p_e$  is then derived from speedup  $s_e$  as:

$$p_e = \frac{1/s_e - 1}{1/n_k - 1}$$

Amdahl's law does not consider cache coherency and memory access in general, which affect estimations based on actual performance measurement. Gunther presented the Universal Scalability Law, which extends Amdahl's model of scalability by contention penalty  $0 \le \alpha$  and coherence penalty  $\beta < 1$  [Gun93]:

$$C(n) = \frac{n}{1 + \alpha(n-1) + \beta \cdot n(n-1)}$$

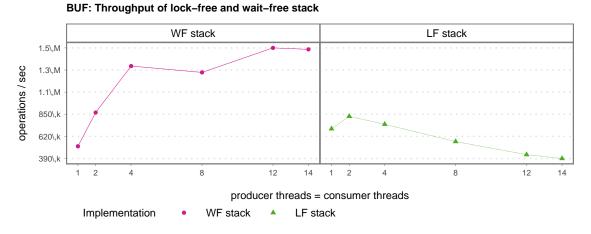

These models are not to be used to curve-fit measurements, but help to discuss observed differences in performance of candidate algorithms. In particular, Gunther's law explains how throughput can actually worsen when a problem is distributed to an increasing number of cores. In fact, this phenomenon will later be observed in evaluation in several cases.

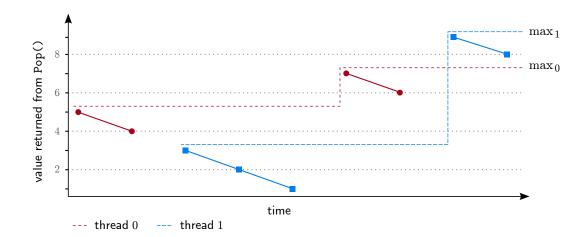

In literature and related work, performance evaluations of data structures typically rank candidates exclusively on average measures, such as the mean throughput |op|/sec, an arguably sensible initial performance indicator for container types. Publications on waitfree algorithms follow this convention and disregard latency measurements completely. All known publications on wait-free algorithms only discuss averaged throughput measurements [KP11] [ZZY+13], despite guaranteed global progress and bounded time to completion being the actual benefit of wait-freedom.

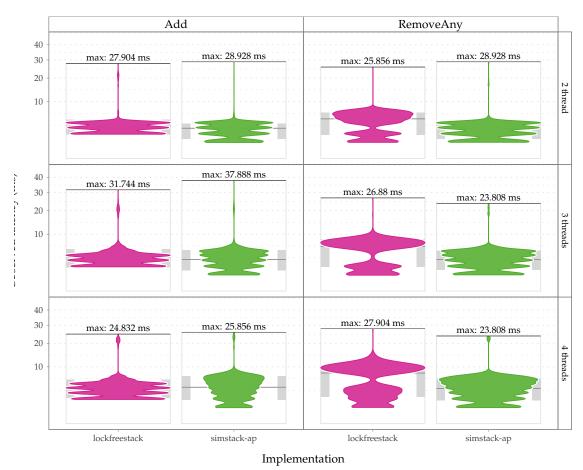

For the data structures presented in the following, worst-case performance is interpreted from measurements in addition to average costs. To give an intuition for complexity overhead of wait-free implementations compared to their lock-free alternatives, verification and evaluation will also include popular lock-free implementations. The benchmark scenarios and the performance metrics include the methods typically found in related publications, disregarding their significance for wait-freedom or applicability on embedded systems. Some test scenarios are not even representative for any realistic use case, but pose an informal standard as they are used in many published evaluations. Results from these benchmarks are presented to allow comparison with results published in related work.

A consolidated metric of worst-case latency is not provided in any related work. Presumably, this is because operation latency highly depends on the test environment and hence measurements are difficult to reproduce. As a matter of fact, distribution of latency is the most valuable metric when deciding for an algorithm in embedded applications. More precisely, worst-case latency is the single criterion to decide if a candidate implementation is better suited than another to meet critical deadlines within hard-timed control loops. For this reason, experiments in this work are also performed on a complementary setup specifically configured for latency measurements.

### **Experimental setup**

We conducted performance evaluation of candidate implementations in this work based on measurements of *throughput* and *latency*. Benchmarks have been performed on two system configurations, each chosen and configured for a specific performance metric:

- AMD Opteron 48-core, 1.9 GHz AMD Opteron 6168, NUMA, Linux 3.11.0-26-generic kernel. Memory access adds non-deterministic latencies on this platform, but the high number of available cores allow **throughput measurements** varying in degree of parallelism.

- **ARM Cortex-A9** 4-core, 996 MHz ARM Cortex-A9, SMP. Configured for **latency measurements**, with a minimal Linux installation and hardware interrupts disabled where possible.

The basis of evaluation are experiments executed on a benchmark suite that has been specifically designed for this work. Its mandatory parameters to execute a benchmark are:

| u                              | the concrete implementation variant (unit) to test. Implicitly also defines available benchmark scenarios. |

|--------------------------------|------------------------------------------------------------------------------------------------------------|

| S                              | the benchmark scenario to execute.                                                                         |

| n <sub>T</sub>                 | the number of threads operating on the shared container in total, or                                       |

| n <sub>P</sub> ,n <sub>C</sub> | the number of producer and consumer threads, if applicable                                                 |

| с                              | the number of elements managed by the data structure, or container                                         |

|                                | capacity                                                                                                   |

| i                              | the number of iterations, configuring how many times each thread exe-                                      |

|                                | cutes its operation sequence.                                                                              |

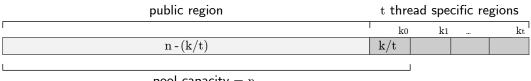

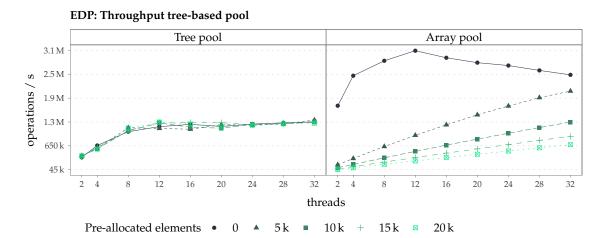

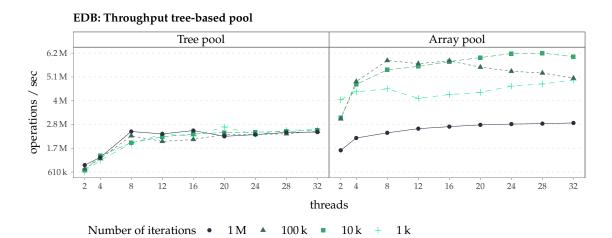

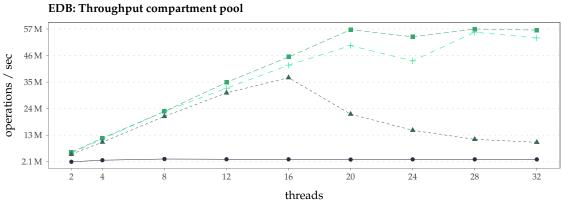

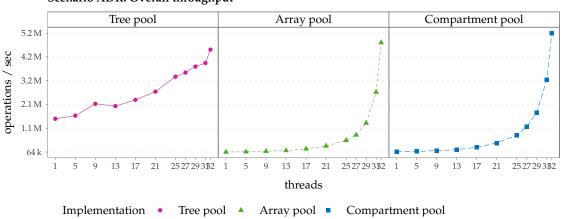

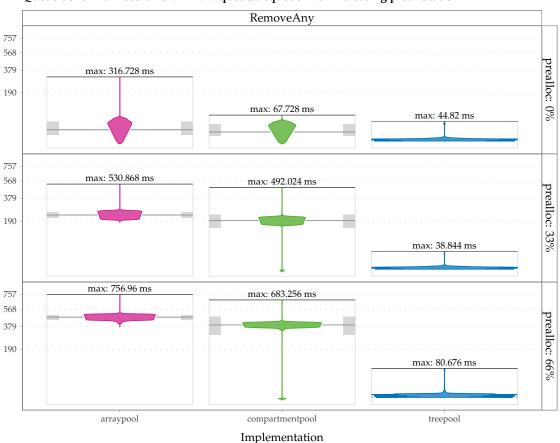

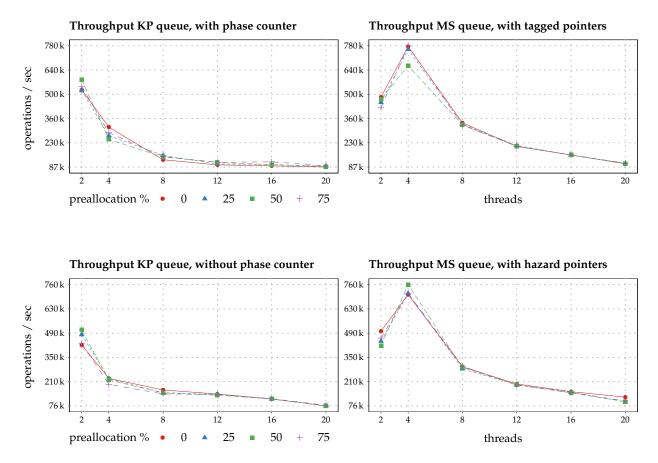

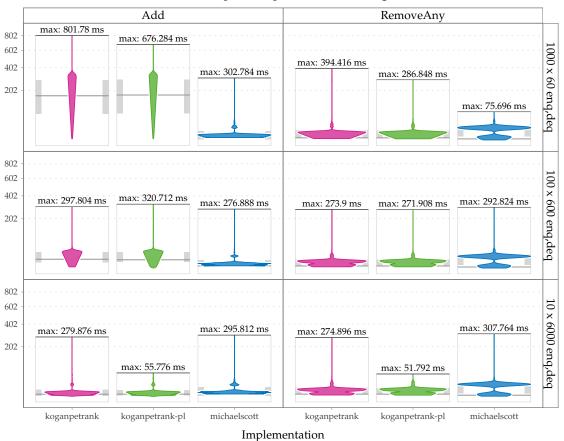

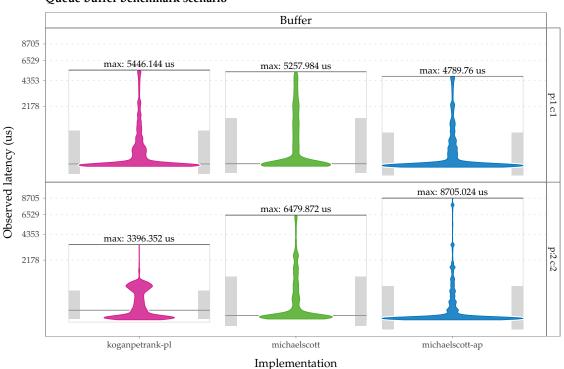

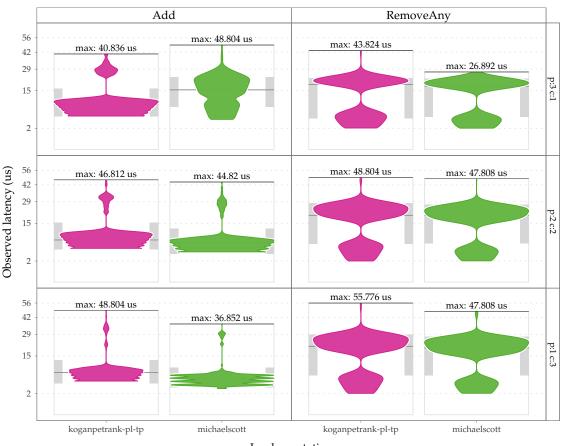

The benchmark suite provides platform-independent, reproducible time measurements, utilizing the most precise performance counters (native constant *Time Stamp Counter*) and wall-clock time available on each of the test platforms. Integrated self-test routines help to ensure correct functionality of internal methods used to measure performance